Posts

233Following

190Followers

181Gabriele Svelto

gabrielesvelto@mas.toOK #Firefox users, this is a special request. I'm looking for someone with a high-end Raptor Lake machine that is experiencing instability in Firefox (or anything else for the matter). The best candidate is a CPU from the 13900* SKUs. K or not doesn't matter as long as it's one with the 8P+16E cores.

We have a potential workaround for one of the most common bugs of this CPU, but we need a broken machine to test it.

Not Just Bikes 🇳🇱

notjustbikes@notjustbikes.comDoes this count as a recession indicator? 😬

For context, when you unsubscribe from someone's Patreon account you are asked for your reason for why you're leaving, and these are summarised for the creator in the "exit interviews" section. This is a screenshot from that.

These days basically everyone is choosing the reason of "My financial situation has changed".

Nick Desaulniers

llvm@fosstodon.org> GNU Emacs, which is a sort of hybrid between Windows Notepad, a monolithic-kernel operating system, and the International Space Station. It’s a bit tricky to explain

https://steve-yegge.medium.com/dear-google-cloud-your-deprecation-policy-is-killing-you-ee7525dc05dc

Laughs in vim

hahaa! Successfully removed all IR and UV filters from my old Canon EOS 600D, I can do full spectrum, UV and IR photography now!

All of the following photos have been taken with a ~550nm+ lpf, meaning cutting everything under 550nm (blue, purple and uv) off. I love the vibrant pink foliage and dramatic turquoise skies #photography

Ian Kluft ✅🖥️📡

KO6YQ@pnw.zoneMay 2026 Portland Linux Kernel Meetup will be Thu May 14 from 6-9pm at Lucky Labrador🐶 Beer Hall, 1945 NW Quimby St, Portland, Oregon 97209. Look for a table with a Linux Tux penguin🐧 plushie.

event page: https://ikluft.github.io/pdx-lkmu/may-2026-portland-linux-kernel-meetup.html

iCal import/subscribe: https://ikluft.github.io/pdx-lkmu/calendar.ics

Calagator (Portland tech events) calendar: http://calagator.org/events/1250482564

organizers: @pdp7 @jstultz @KO6YQ

#PDXLKMU #PDX #Portland #Oregon #Linux #Kernel #OpenSource #software #engineering #tech #PNW

Ben Lockwood, PhD

benlockwood@ecoevo.social“AI is here to stay” says the makers of NFTs, the metaverse, Google Glass, Windows Phone

Filippo Valsorda

filippo@abyssdomain.expertThere are no technical or compliance reasons to double the size of symmetric keys in response to the threat of quantum computers.

This common misunderstanding of Grover's algorithm risks wasting limited resources that should go towards deploying actually urgent post-quantum algorithms.

The War on Cars

TheWarOnCars@mastodon.socialIt's been exactly 6 months since LIFE AFTER CARS was published.

Our book tour has taken us to 27 cities around North America and seen us do more than 100 press interviews with many more to come.

Thanks to everyone who's bought the book and spread the word!

mjw

mjw@mastodon.nl#valgrind 3.27.0 released!

New options for helgrind (--show-events and --track-destroy), new SSE4.1 instruction for x86, support for s390x z/Architecture features from 15th edition, integrated binutils objdump for s390x disassembly, new linux syscalls, address space manager tracking linux kernel lightweight guard pages, freebsd 16.0-CURRENT, macOS up to version 13 Ventura (Intel), new client requests (VALGRIND_REPLACES_MALLOC, VALGRIND_GET_TOOLNAME).

https://gnu.wildebeest.org/blog/mjw/2026/04/20/anticipating-valgrind-3-27-0/

Oleksandr Natalenko, MSE

oleksandr@natalenko.name

The previous section covered RCU grace-period detection based purely on time. But a recent discussion with Hui Xie led me to wonder about instead basing them purely on space

And this is how the RCU space-time curvature was discovered.

https://people.kernel.org/paulmck/stupid-rcu-tricks-corner-case-rcu-implementations

Carlos O'Donell

codonell@fosstodon.org"The GNU libc atanh is correctly rounded." (https://inria.hal.science/hal-05591661) That simple phrase is so exceedingly hard to prove, and yet we chase the goal because some workloads require it and we can achieve this goal in some cases without worst case performance loss. For glibc 2.43 the project has integrated 32 of the CORE-MATH library functions.

Kees van der Leun

Sustainable2050@mastodon.energyIt looks like Dutch government will avoid the unbearable dumbness of lowering fuel taxes amid a supply crisis! More sensible measures include compensating kilometers driven for work, support for low income households, and more subsidies for insulating homes.

https://nos.nl/artikel/2610433-kabinet-komt-met-steunpakket-van-1-miljard-euro-maar-benzine-niet-goedkoper

Mastodon

Mastodon@mastodon.socialWe’re happy to share that Mastodon has been awarded a service agreement from the Sovereign Tech Fund @sovtechfund 🎉

This covers five major initiatives through 2026 and 2027. We are very grateful for this support. Read about the details in our blog post.

https://blog.joinmastodon.org/2026/04/sovereign-tech-agency-funding/

gigabecquerel

gigabecquerel@chaos.socialI don't want to drink alone, but I do enjoy a "post work drink". So I buy alcohol free beers for those occasions. Tried this IPA today, and I really like it!

Definitely will pick up a crate next time.

Krister Walfridsson

kristerw@mastodon.gamedev.placeI wrote a blog post about how smtgcc, my GCC translation validator, handles uninitialized memory.

https://kristerw.github.io/2026/04/10/uninitialized-memory/

mid_kid

mid_kid@fosstodon.org#gentoo #portage feature I learned about today by accident:

emerge --pretend --fetchonly (shortened as emerge -pf) will print all the URLs it'd use to download the various distfiles, instead of listing the results of the dependency resolution (as --pretend would usually do).

Caught me off-guard, I don't think this is documented anywhere. Glad to know portage still hits me with surprises after using it for 7 years 😅

Positive News: France has announced its plan to ditch Windows & switch to Linux for government desktops. 🥳 🇫🇷

Not only that, but they have also moved 80, 000 National Health Insurance Fund Employees to open source alternatives replacing U.S owned Big Tech platforms like Microsoft Teams & Zoom.

It’s amazing to see the country take action, push for real digital sovereignty, & opt for open source solutions! 👏

Filippo Valsorda

filippo@abyssdomain.expertTwo papers came out last week that suggest classical asymmetric cryptography might indeed be broken by quantum computers in just a few years.

That means we need to ship post-quantum crypto now, with the tools we have: ML-KEM and ML-DSA. I didn't think PQ auth was so urgent until recently.

Michael Opdenacker

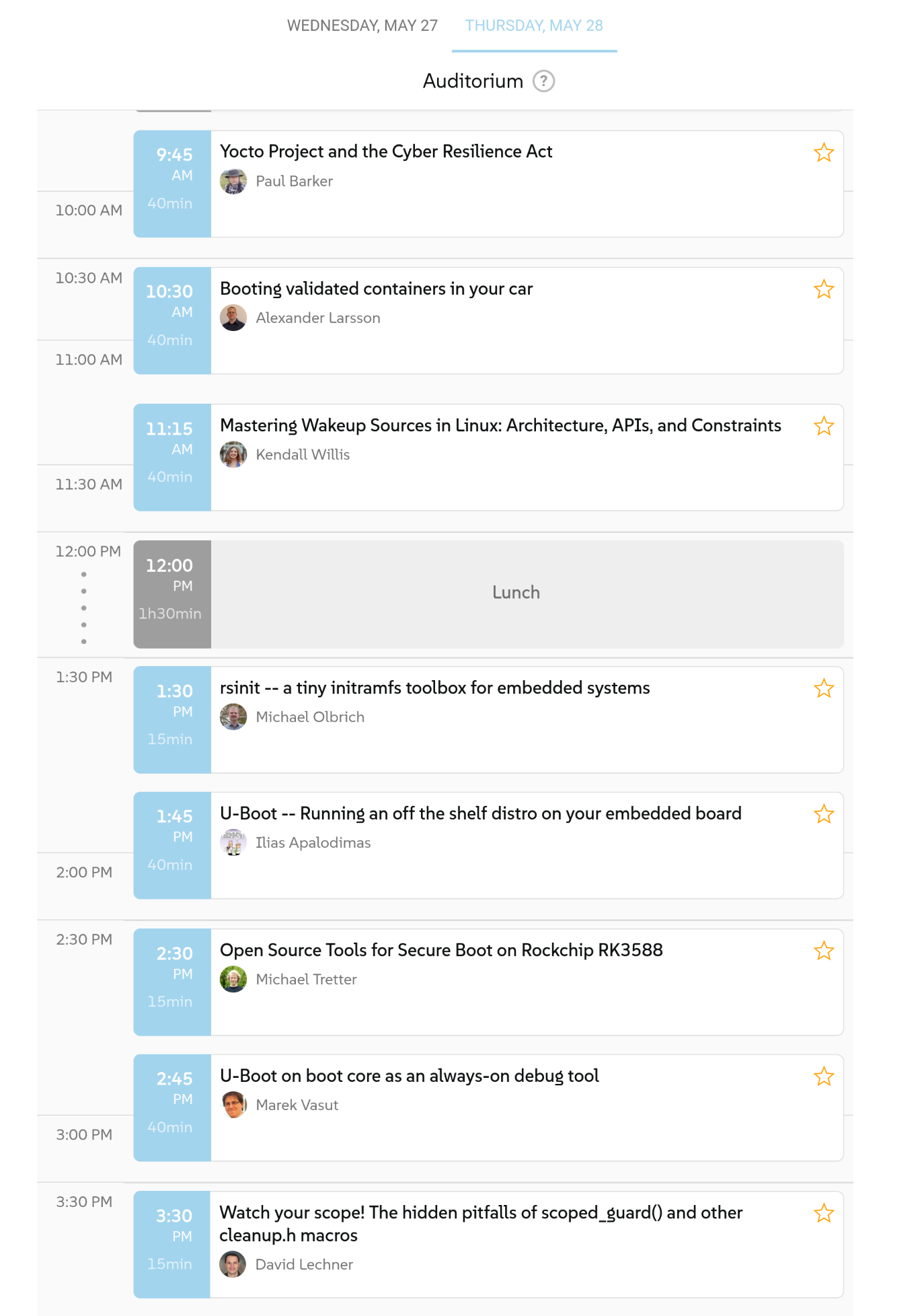

MichaelOpdenacker@fosstodon.orgThe schedule of the upcoming "Embedded Recipes" conference (May 27-28, Nice, France) is available. A fine selection of topics and speakers!

I hope to see many of you there, and don't forget the Yocto day on May 29, which schedule is expected in 4 days (Apr. 10).