Posts

5470Following

347Followers

543Jarkko Sakkinen

jarkko

Multi-core was already a thing (and Moore's law for single core was reached) when wasm was invented and its execution pipeline is really better fit for hardware that precursors it by multiple years.

Jarkko Sakkinen

jarkko

Edited 5 months ago

@pinkforest well yeah of course you need to address contraints when designing "softcore" (i guess this a term?) :-)

First, you need some register space for book keeping (like one or two registers at least) and it unfortunately shares space with softcores registers.

So problem at hand is like:

1. Reduce softcores register space i.e., it will have less registers than host CPU.

2. "Share-and-swap" registers with the softcore for the colliding part.

This of course assumes that ISA is similar enough to x86-64 and aarch64 but that is quite fair constraint to set from the get go for obvious reasons :-)

Anyhow, it will quite simple and sound translation with no artificial stack machines blocking the way :-)

First, you need some register space for book keeping (like one or two registers at least) and it unfortunately shares space with softcores registers.

So problem at hand is like:

1. Reduce softcores register space i.e., it will have less registers than host CPU.

2. "Share-and-swap" registers with the softcore for the colliding part.

This of course assumes that ISA is similar enough to x86-64 and aarch64 but that is quite fair constraint to set from the get go for obvious reasons :-)

Anyhow, it will quite simple and sound translation with no artificial stack machines blocking the way :-)

Jarkko Sakkinen

jarkko

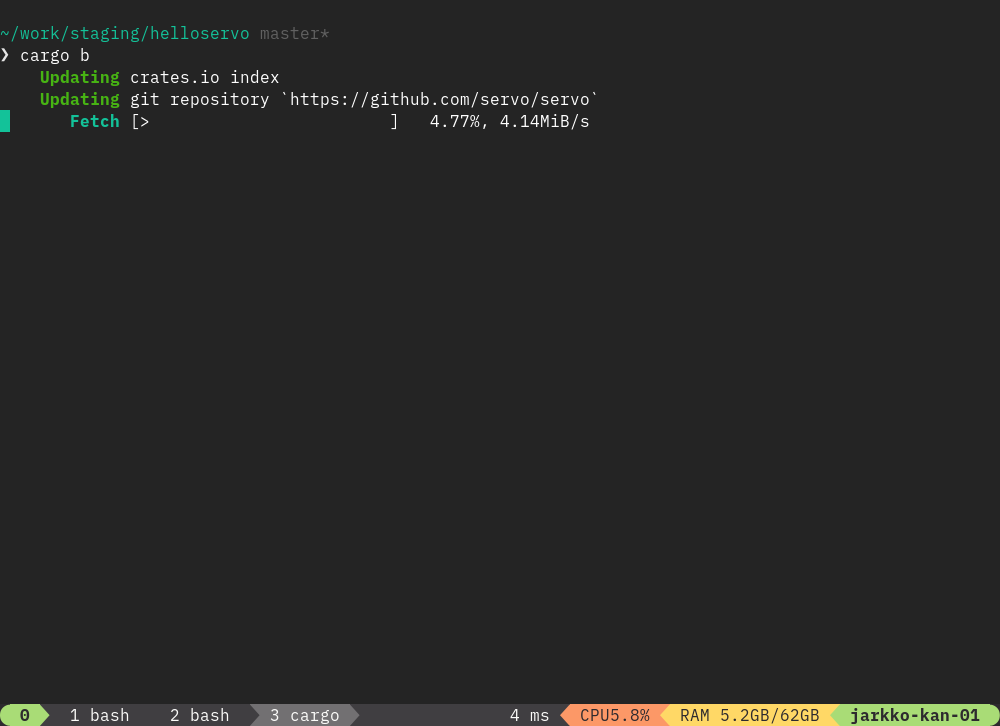

I'm using Servo in the next (0.3.x) version of mailweb, which will no longer open browser like viewhtmlmail.

Instead using servo this will happen when showing HTML mail in mutt:

1. Render page as bitmap(s) to the cache after extracting CID shenanigans using Servo.

2. Page is showed then in the terminal sixel first and fallback to unicode rendering.

This way sixels performance issues won't get in the way and will overall much nice experience than opening a random tab in a browser.

https://crates.io/crates/mailweb

#mutt #viewhtmlmail #mailweb #servo

Instead using servo this will happen when showing HTML mail in mutt:

1. Render page as bitmap(s) to the cache after extracting CID shenanigans using Servo.

2. Page is showed then in the terminal sixel first and fallback to unicode rendering.

This way sixels performance issues won't get in the way and will overall much nice experience than opening a random tab in a browser.

https://crates.io/crates/mailweb

#mutt #viewhtmlmail #mailweb #servo

Jarkko Sakkinen

jarkko

there's now easy path to get #servo webviews: https://github.com/nacho/servo-gtk

Jarkko Sakkinen

jarkko

Edited 5 months ago

@mjg59 i'm also working loosely with oracle to realize d-rtm i.e. trenchboot i.e. lots of stuff is going to get shuffled anyhow and made more robust and early boot friendly etc. so i think the time is right too. and to add, it would good to see it collide with those changes if there is anything because that might help to make right choices with trenchboot related changes.

Jarkko Sakkinen

jarkko

@mjg59 and also i'm waiting for situations like this to further refine my small debugging tool for tpm (initated in august): https://crates.io/crates/tpm2sh

Jarkko Sakkinen

jarkko

Edited 5 months ago

@mjg59 please do send patches, in my books it would be feasible feature, and would be also interesting to wire hat up to my buildroot build and vm setup, and a find way to get fast edit-compile-run cycle :-) not promising ack but i can commit with this message to test run it live before giving even a single review comment because it would be a fun challenge.

Jarkko Sakkinen

jarkko

Edited 5 months ago

WebAssembly is one of the worst ideas in the industry during past 10 years. why end up with stack machine and purposely complicate JIT. Never really grabbed it engineering wise TBH but maybe I'm missing something who knows.

You don't need to be an engineer to get it. It just tends to be easier to find ways map registers to registers, and requires more stretch to move between stack and register machine.

You don't need to be an engineer to get it. It just tends to be easier to find ways map registers to registers, and requires more stretch to move between stack and register machine.

Jarkko Sakkinen

jarkko

@oleksandr it's entertaining and it has been nice to hook with some old friends so definitely on plus side :-)

Jarkko Sakkinen

jarkko

Edited 5 months ago

linkedin i scroll posts and spot at least three posts from someexperts about DAC permission and how to decipher them.

dude, you have like left and right plus one more state. i could explain DAC to my mom who does not anything aboutc omputers or permissions and i'm confident that she would get it.

other posts are the usual 2025 AI crap. i made account mostly to backup CV somewhere someday and curiosity after many years away from.

it does deliver shit and i do get some entertainment for boring moments so i guess it is a great service then 🤷

dude, you have like left and right plus one more state. i could explain DAC to my mom who does not anything aboutc omputers or permissions and i'm confident that she would get it.

other posts are the usual 2025 AI crap. i made account mostly to backup CV somewhere someday and curiosity after many years away from.

it does deliver shit and i do get some entertainment for boring moments so i guess it is a great service then 🤷

Jarkko Sakkinen

jarkko

"I’m not glad he’s dead, but I’m glad he’s gone.”

https://www.reuters.com/world/us/former-us-vp-dick-cheney-dead-84-punchbowl-news-says-2025-11-04/

https://www.reuters.com/world/us/former-us-vp-dick-cheney-dead-84-punchbowl-news-says-2025-11-04/

Jarkko Sakkinen

jarkko

split zmodem2 into two separate projects:

1. https://crates.io/crates/zmodem2

2. https://crates.io/crates/lrzsz2

this will still need a lot of love before being a production tool but working batch transfers (against lrzsz) is good start.

1. https://crates.io/crates/zmodem2

2. https://crates.io/crates/lrzsz2

this will still need a lot of love before being a production tool but working batch transfers (against lrzsz) is good start.

Jarkko Sakkinen

jarkko

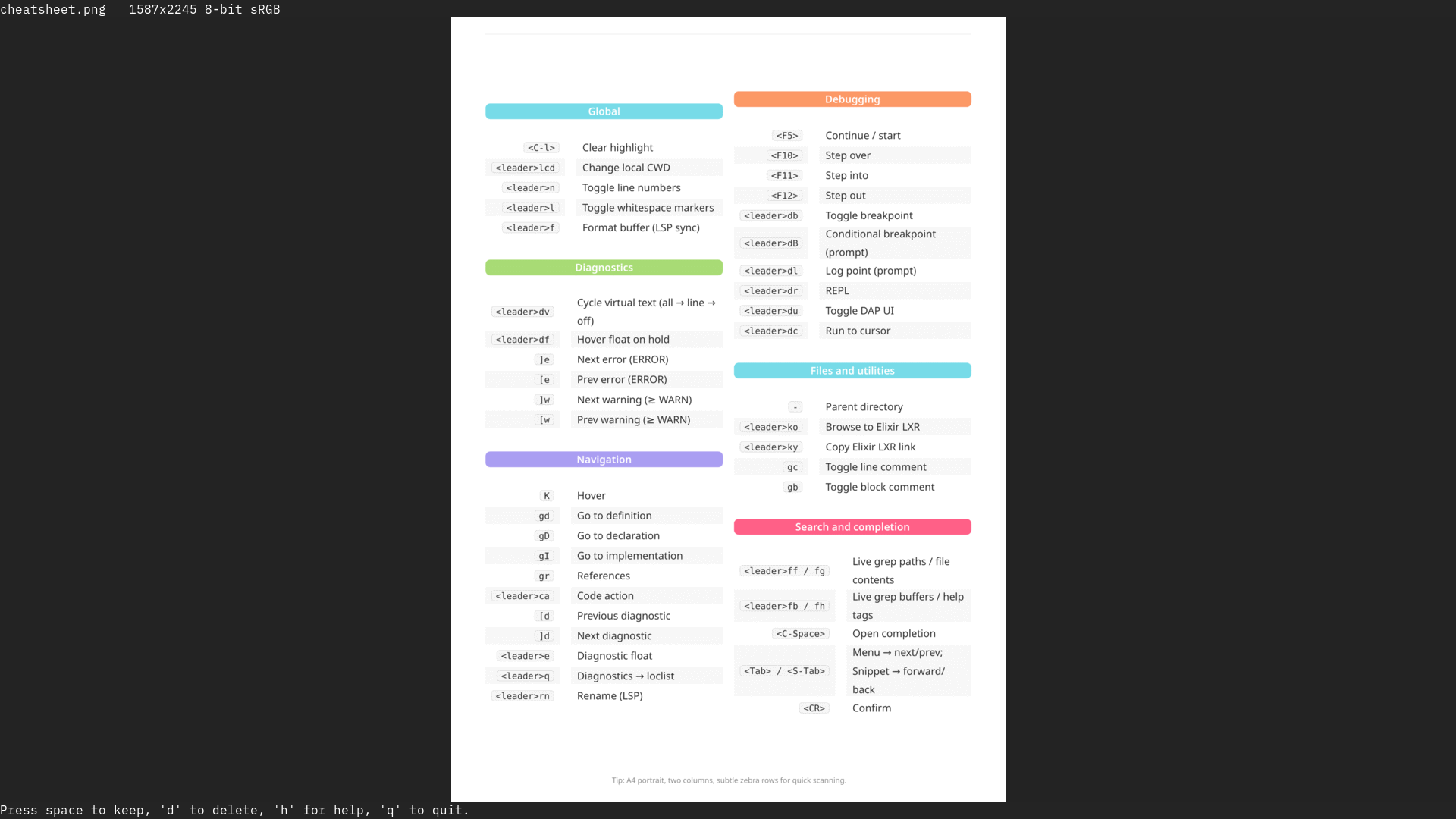

I created a cheat sheet of my accumulated custom shortcuts in vim using typst. i'm going to maintain this and capping custom shortcuts to fit into single A4 helps to make sure that things don't get too complicated :-)

Jarkko Sakkinen

jarkko

going to submit a talk next year to the first linux security summit cfp :-)

Jarkko Sakkinen

jarkko- https://crates.io/crates/tpm2sh

- https://crates.io/crates/tpm2-protocol

- https://crates.io/crates/tpm2-crypto

- https://crates.io/crates/tpm2-policy-language

- https://crates.io/crates/tpm2-tpmkey

i guess you can call this a “developer ecosystem” :-)