Posts

671Following

107Followers

127- Linux Kernel Developer @ Oracle (Linux Kernel MM) (2025.02 ~ Present)

- A slab subsystem co-maintainer and a reviewer for the reverse mapping subsystem

- Former Intern @ NVIDIA, SK Hynix, Panmnesia (Security, MM and CXL)

- B.Sc. in Computer Science & Engineering, Chungnam National University (Class of 2025)

Opinions are my own.

My interests are:

Memory Management,

Computer Architecture,

Circuit Design,

Virtualization

Harry (Hyeonggon) Yoo

hyeyooJames Bottomley

jejb@mastodon.online@linuxplumbersconf Youtube Live Stream URLs are now available on the Schedule Overview page (https://lpc.events/event/17/timetable/#all).

Find the track you want and click the paperclip on the upper right corner to bring up the Live Stream Link

Harry (Hyeonggon) Yoo

hyeyoo2 months is bit short for a project, so we need to find a very small question that no one has answered.

It seems I've found a question suitable for our need in the compiler area, but I need to consult with the professor to verify if it's a valid question.

Harry (Hyeonggon) Yoo

hyeyooHarry (Hyeonggon) Yoo

hyeyooShould've realized that I can't have both :(

Harry (Hyeonggon) Yoo

hyeyoo1) As an extended capability in PCIe extended configuration space, (Designated) Vendor-Specific Extended Capabilities can be used to access vendor-specific registers. As more than one vendor produces CXL devices, DVSEC is used instead of VSEC.

2) BARs can be used to map device resources (registers or memory) into system memory address space.

Errrr.. btw many registers are there in the CXL spec :/

Notably:

- (DVSEC) "PCIe DVSEC for CXL Device" is used to identify CXL-capable PCIe endpoints

- (DVSEC) "Register Locator DVSEC" is used to locate CXL memory-mapped registers

- (Memory-Mapped) "CXL 2.0 Component Registers" is used to configure CXL Components (Host Bridge, Root Port, Upstream/Downstream Port, Device)

- (Memory-Mapped) "CXL Device Register Interface" is used to access CXL device registers and issue commands to a CXL device

Configuration space of Every CXL 2.0 component can be accessed via the standard PCIe method, except Host Bridges. Component Registers of CXL Host Bridges are located by ACPI CEDT table, which also contains CFMWS (CXL Fixed-Memory-Window Structure).

Kees Cook (old account)

kees@fosstodon.orgHere's how to enable the kernel Memory Tagging Extension (#MTE) on the Pixel 8:

adb shell setprop arm64.memtag.bootctl memtag,memtag-kernel

I'm so happy there's real-world hardware finally available to provide mitigations against linear buffer overflows and many types of use-after-free flaws.

More details here:

https://outflux.net/blog/archives/2023/10/26/enable-mte-on-pixel-8/

Harry (Hyeonggon) Yoo

hyeyooHarry (Hyeonggon) Yoo

hyeyooWhy can't UEFI (Unified EFI) unify everything :/

Harry (Hyeonggon) Yoo

hyeyooThis whole question may be wrong as Iack some knowledge about it.

Harry (Hyeonggon) Yoo

hyeyooHarry (Hyeonggon) Yoo

hyeyooHow have people been reading this?

Harry (Hyeonggon) Yoo

hyeyooHarry (Hyeonggon) Yoo

hyeyooAn OS loader reads information such as ACPI tables, memory maps, etc. through UEFI and passes it to OS, which then takes over control. Most of the services provided by UEFI, including the ACPI Table and Memory Map, are not accessible after OS loader calls the UEFI's Boot Service ExitBootServices().

Intel provides open source reference implementations of firmware that adhere to the UEFI standard called EDK 2. The firmware also implements PCI host bus controllers, bus drivers, and device drivers.

In order to add CXL memory to the memory map during system initialization, the firmware must have CXL support added so that you can set up a CXL host bridge, switch, and device at system initialization before OS has taken the control.

Harry (Hyeonggon) Yoo

hyeyooACPI HMAT describes latency/bandwidth characteristics.

CDAT is a set of registers in CXL that reports bandwidth/latency characteristics of CXL devices/switches. it is consumed by firmware to produce HMAT/SRAT tables.

Harry (Hyeonggon) Yoo

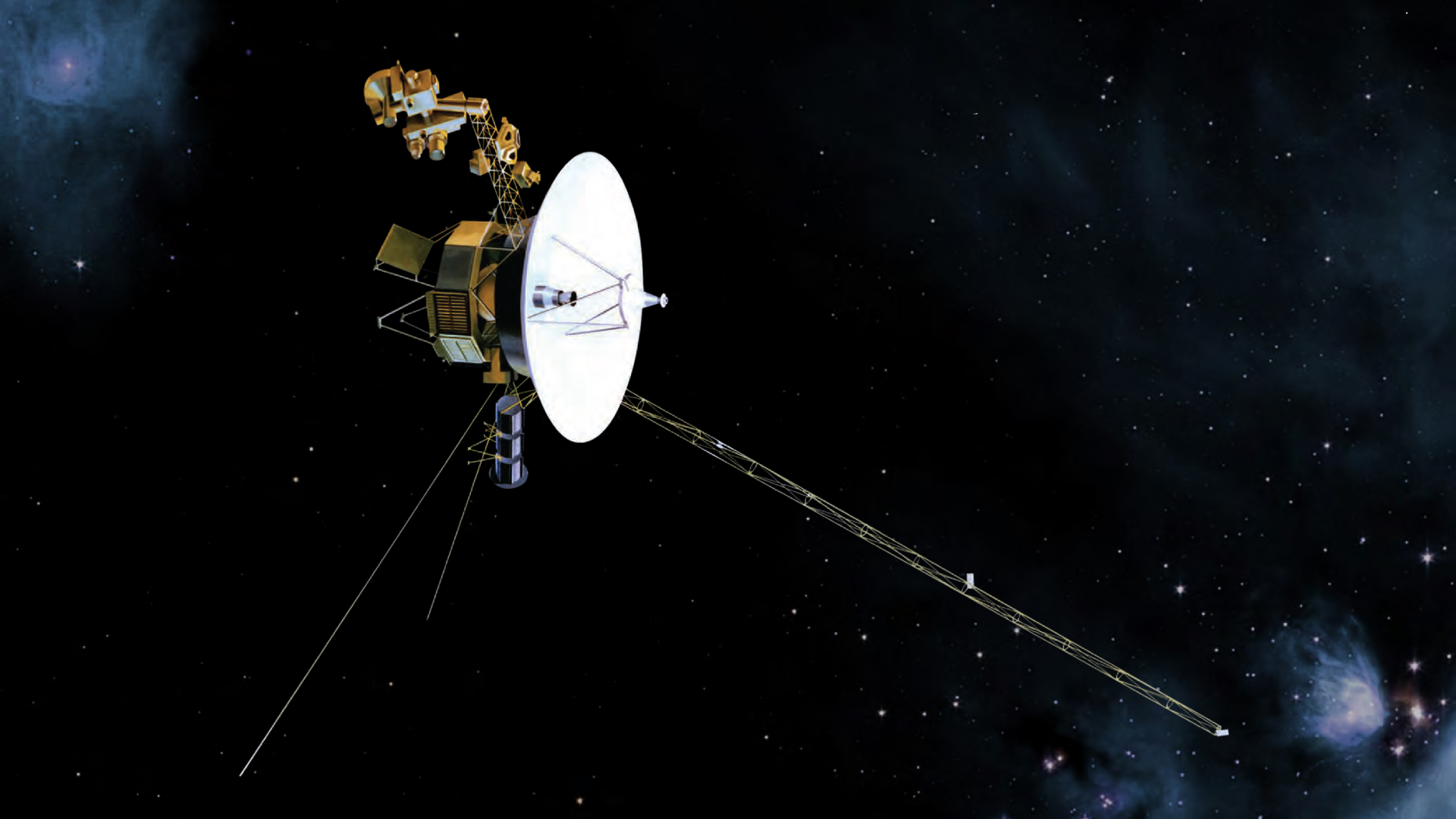

hyeyooAkaSci 🛰️

AkaSci@fosstodon.orgNASA is sending a software update to the Voyager 2 spacecraft today!

Data will be sent at 16 bps with a 19 kW transmitter using the 70-m dish at DSN Canberra.

Distance: 20 billion km

Light travel time: 18:40 hours

The patch contains logic to recover from glitches similar to the one in May 2022, when the AACS system on Voyager 1 was sending garbled data. The root cause was not diagnosed. The patch will be activated on Oct 28. Voyager 2 will be next.

https://www.jpl.nasa.gov/news/nasas-voyager-team-focuses-on-software-patch-thrusters

#Voyager

1/n